Методичні вказівки щодо проведення лабораторної роботи "Дослідження логічних ІМС типу ТТЛ"

1

Дисципліна: "Комп’ютерна логіка та схемотехніка"

МЕТОДИЧНІ ВКАЗІВКИ ЩОДО ПРОВЕДЕННЯ ЛАБОРАТОРНОЇ РОБОТИ

"ДОСЛІДЖЕННЯ ЛОГІЧНИХ ІМС ТИПУ ТТЛ"

Мети роботи: - вивчити структуру логічних ІМС типів ТТЛ на прикладі мікросхеми К155ЛА3 (SN7400);

- вивчити функції, що виконуються логічними ІМС;

- дослідити основні параметри логічних мікросхем К155ЛА3 (SN7400).

Короткі теоретичні відомості

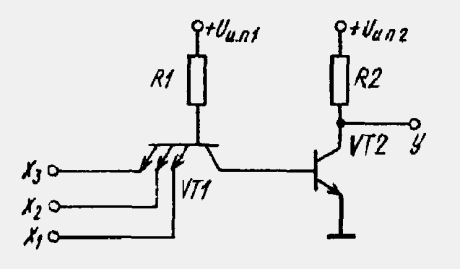

ТТЛ-схемами прийнято називати такі логічні ІМС, у яких логічна операція кон’юнкції виконується за допомогою багатоемітерного транзистора npn-типу.

На рисунку 1 показаний найпростіший варіант схеми ТТЛ, що виконує функцію І-НІ. Якщо на усі входи схеми, тобто на емітери багатоемітерного транзистора типу npn, подані позитивні напруги, що відповідають логічній одиниці, то емітерні переходи зміщаються в зворотному напрямку.

На рисунку 1 показаний найпростіший варіант схеми ТТЛ, що виконує функцію І-НІ. Якщо на усі входи схеми, тобто на емітери багатоемітерного транзистора типу npn, подані позитивні напруги, що відповідають логічній одиниці, то емітерні переходи зміщаються в зворотному напрямку.

Рисунок 1- Принципова схема одного логічного елемента ІМС типу ТТЛ

Струм, що надходить у базу багатоемітерного транзистора VT1 через резистор R1, проходить у коло колектора, зміщеного в прямому напрямку, і далі в базу транзистора, що інвертує, VT2. При цьому транзистор VT2 переходить у режим насичення, а напруга на виході схеми відповідає логічному нулю.

Якщо хоча б на один вхід подана напруга логічного нуля, то відповідний емітерний перехід транзистора VT1 зміщається в прямому напрямку. Струм, що надходить у базу транзистора VT1, буде переважно проходити через цей перехід. Колекторний струм транзистора VT1 зменшується, і транзистор VT2 замкнеться, тому що струм у його базі стане менше порога включення. На виході схеми напруга підвищиться до рівня логічної одиниці.

Перевага схеми ТТЛ перед іншими типами логічних ИМС полягає в їхній високій швидкодії, заснованій на активній дії механізму переключення вхідного транзистора. У процесі запирання транзистора VT2 заряд, накопичений у його базі, розряджається через вхідний транзистор, чим забезпечується його активне розсмоктування.

Недоліками схеми ТТЛ із простим інвертором є низька перешкодостійкість (Uп = 0,2...0,3 В) через низьку напругу відмикання транзистора, що інвертує, а також невелика навантажувальна здатність (Кроз = 4…6). Ці недоліки усуваються в схемах ТТЛ зі складним інвертором (див. рисунок 2). Ці схеми володіють підвищеної перешкодостійкістю (Uп = 0,7…1 В) і навантажувальною здатністю (Кроз = 10...15).

Рисунок 2 - Схема ТТЛ зі складним інвертором

Параметри ІМС підрозділяються на дві групи - статичні і динамічні.

Статичні параметри характеризують роботу ІМС при статичних логічних 0 чи 1 на вході і виході.

До статичних параметрів відносяться:

1. Напруга джерела живлення Uдж.

2. Вхідні і вихідні напруги логічного нуля і логічної одиниці: Uвх0, Uвх1, Uвих0, Uвих1.

3. Коефіцієнт розгалуження Кроз показує кількість входів мікросхем навантажень, який можна підключити до даної мікросхеми без утрати її працездатності (характеризує навантажувальну здатність ІМС).

4. Коефіцієнт об'єднання по входу Коб показує, кількість входів мікросхеми, по яких реалізується виконувана нею функція.

5. Напруга статичної перешкоди Uст.п. - це максимально припустима статична напруга на вході, при якому мікросхема не утрачає свій працездатності. Даний параметр характеризує перешкодостійкість ІМС.

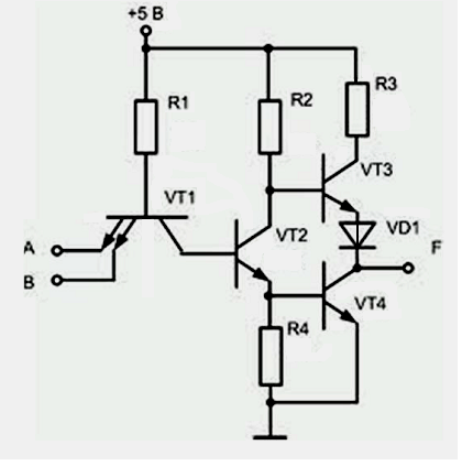

Динамічні характеристики характеризують роботу ІМС у момент переключення з нуля в чи одиницю з одиниці в нуль (див. рисунок 3).

Рисунок 3 – Динамічні характеристики ІМС

Порядок виконання лабораторної роботи

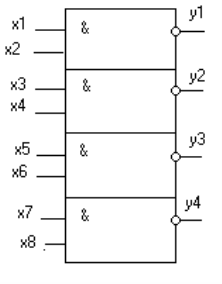

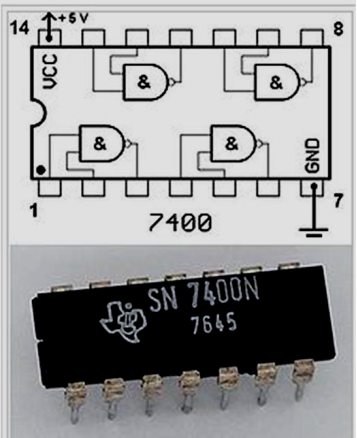

1. Вивчіть конструкцію, функціональну і принципову схеми одного логічного елемента ІМС, що виконує логічну операцію І-НІ, згідно рисунка 2 і рисунка 4.

Рисунок 4 – Конструкція і структурна схема ІМС 7400 (К155ЛА3)

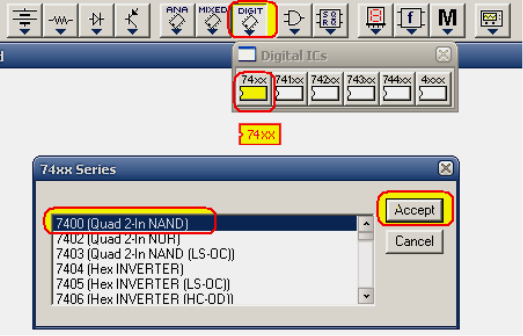

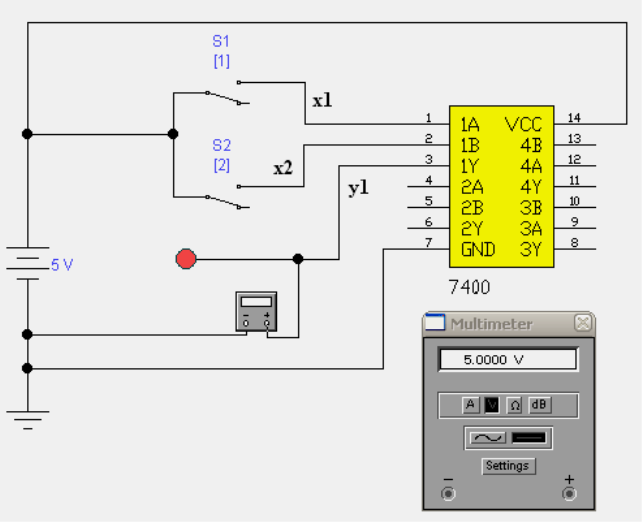

2. Зберіть на робочому полі програми Electronics Workbench (Multisim) схему дослідження логічної ІМС 2І-НІ серії 7400 згідно рисунка 5. Подайте на мікросхему напругу живлення Еживл = +5 В. Підключіть ІМС типу ТТЛ до вимірювальних приладів.

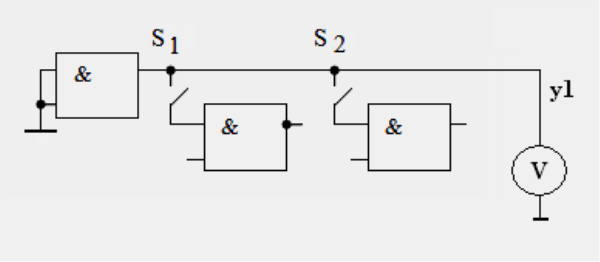

3. Виконайте віміри вихідних напруг Uвих0 и Uвих1 на виході логічного елемента мікросхеми, подаючи на вхід мікросхеми напруги Uвх1 за допомогою тумблерів S1 та S2 (див. рисунок 5).

Рисунок 5 - Схема дослідження логічної ІМС 2І-НІ серії 7400

Результати вимірів занесіть у таблицю 1. Переконайтеся, що логічні елементи мікросхеми здійснюють логічну функцію І-НІ.

Таблиця 1

|

Режим комутації |

Параметр Uвих (у1) |

|

S1 відк. , S2 відк. (х1 = 0, х2 = 0) |

|

|

S1 вкл. , S2 відк. (х1 = 1, х2 = 0) |

|

|

S1 відк. , S2 вкл. (х1 = 0, х2 = 1) |

|

|

S1 вкл., S2 вкл. (х1 = 1, х2 = 1) |

|

Порівняєте отримані результати з довідковими даними мікросхеми К155ЛА3:

Uвих1, не менш - 2,4 В

Uвих0, не більш - 0,4 В

4. Зніміть залежність рівнів вихідної напруги одного з логічних елементів від числа навантажувальних елементів (методика досліду згідно схеми на рисунку 6). Число навантажень - 2.

Результати вимірів занесіть у таблицю 2.

Рисунок 6

Таблиця 2

|

Комутація навантажень |

Значення Uвих1 (y1) |

Параметр |

|

|

Крозг. (дослід) |

Крозг. (паспорт) |

||

|

S1...S2 відк. |

|

|

10 |

|

S1 вкл. S2 відк. |

|

||

|

S1, S2 вкл. |

|

||

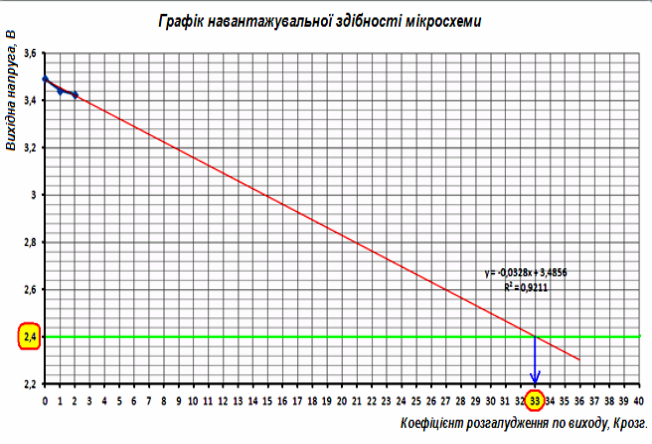

За результатами вимірів побудуйте за допомогою програми Excel лінію тренда і графічно визначите коефіцієнт розгалуження по виходу Кpозг мікросхеми, порівнявши його з паспортними даними мікросхеми К155ЛА3 (Кpозг = 10).

Результат графічного визначення параметра Крозг виконайте згідно рисунку 7.

Рисунок 7 – Графічне визначення параметра Крозг

Зробіть висновок про навантажувальну здатність мікросхеми.

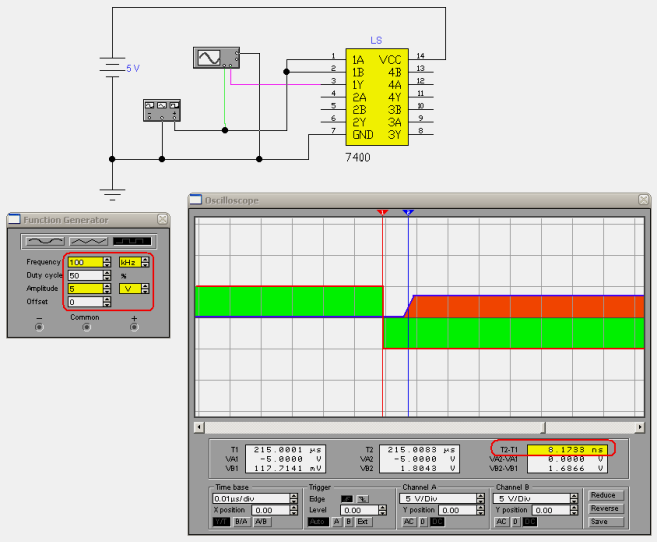

5. Зберіть схему згідно рисунку 8. Подайте на входи логічного елемента прямокутні імпульси і за допомогою осцилографа вимірить параметр ІМС - середній час затримки розповсюдження сигналу tз.p.с.

Результати вимірів занесіть у таблицю 3.

Таблиця 3

|

Назва параметра |

Значення параметра |

|

Середній час затримки розповсюдження сигналу tзд.p.с, нс |

|

Рисунок 8 – Визначення швидкодії ІМС

Порівняєте дослідне значення часу tзд.p.с з довідковими даними мікросхеми К155ЛА3:

tзд.p. l-0, не більш - 15 нс;

tзд.p. 0-1, не більш - 22 нс.

Зробіть висновок про швидкодію мікросхеми.

Зміст звіту з лабораторної роботи

1. Назва і мети роботи.

2. Функціональна і принципова (одного логічного елемента) схеми мікросхеми К155ЛА3.

3. Таблиці вимірів і графік визначення коефіцієнта розгалуження по виходу.

4. Схеми дослідів ІМС.

4. Висновки про результати досліджень.

5. Короткі відповіді на контрольні питання.

Контрольні питання

1. Який є вплив збільшення навантаження на вихідний рівень логічної схеми ТТЛ-типу?

2. Які є способи збільшення швидкодії мікросхем?

Література

- Швець Є. Я., Червоний І. Ф., Головко Ю. В. Матеріали і компоненти електроніки : навчальний посібник. - Запоріжжя : ЗДІА, 2011.

- Гуржій А.М., Поворознюк Н.І. Електричні і радіотехнічні вимірювання / А.М. Гуржій, Н.І. Поворознюк. – Київ: Навчальна книга, 2002.

про публікацію авторської розробки

Додати розробку